在堆叠L3缓存的3D V-Cache技术助其统治游戏CPU市场后,AMD并未止步。近日,AMD公布了一篇名为《均衡延迟堆叠缓存》(Balanced Latency Stacked Cache)的研究论文(专利号US20260003794A1),揭示了其在缓存架构上的下一个计划:堆叠L2缓存。

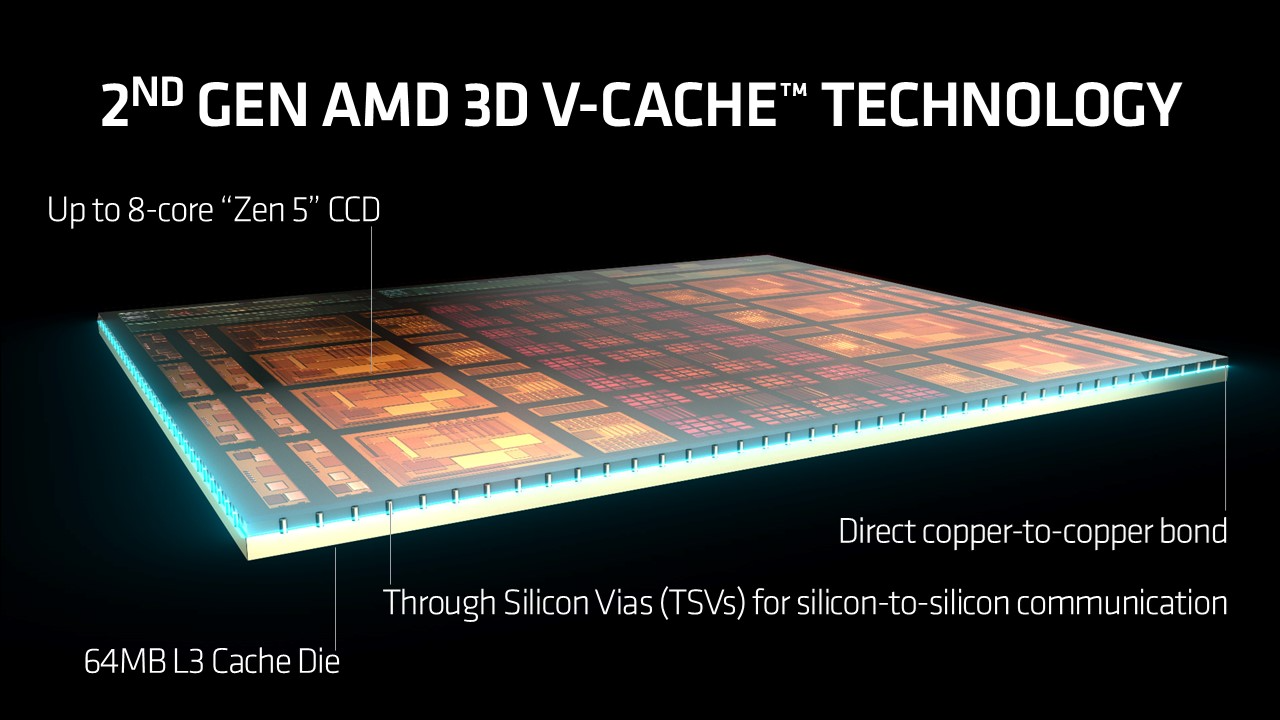

目前的3D V-Cache主要是通过在核心上方或下方堆叠额外的L3缓存来提升性能,而新专利显示,AMD正在探索将堆叠技术引入距离CPU核心更近、响应更快的L2缓存。

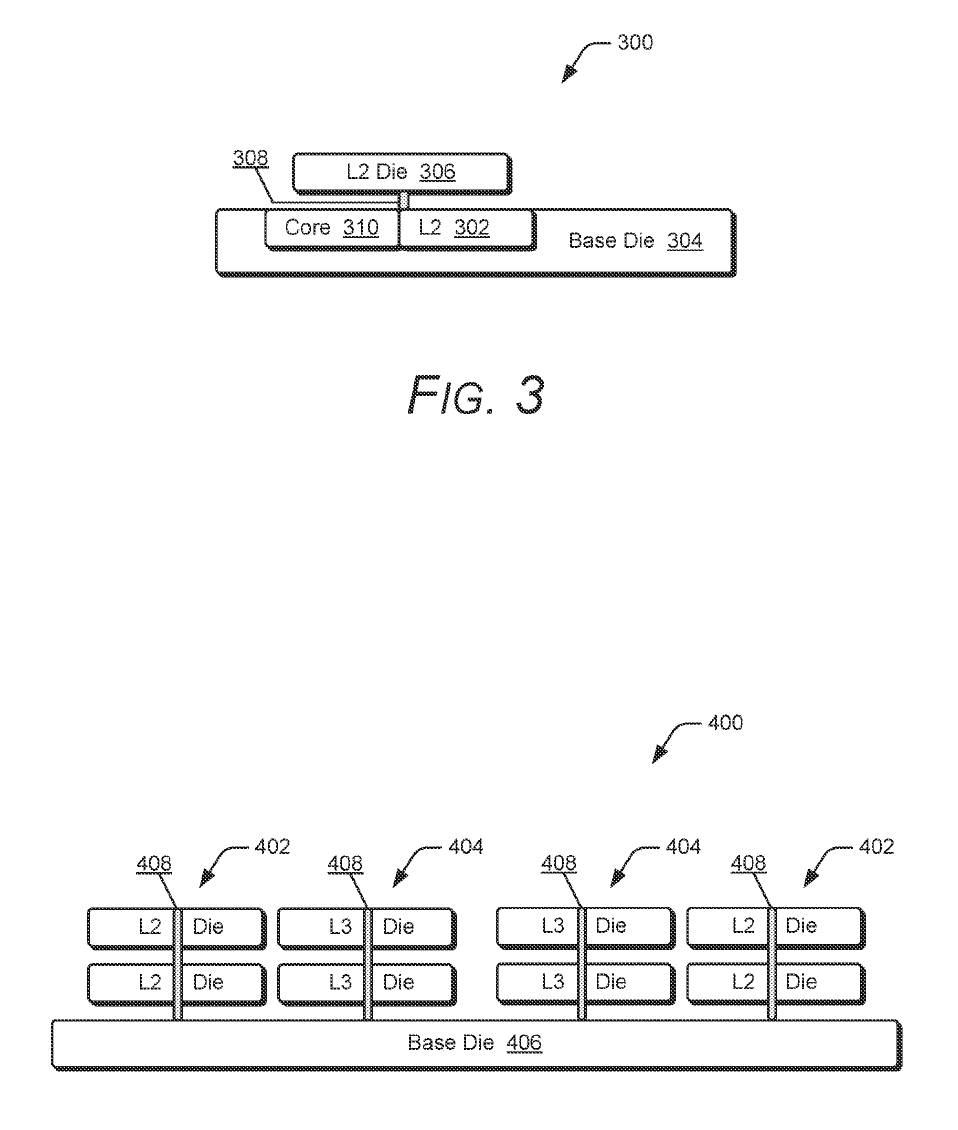

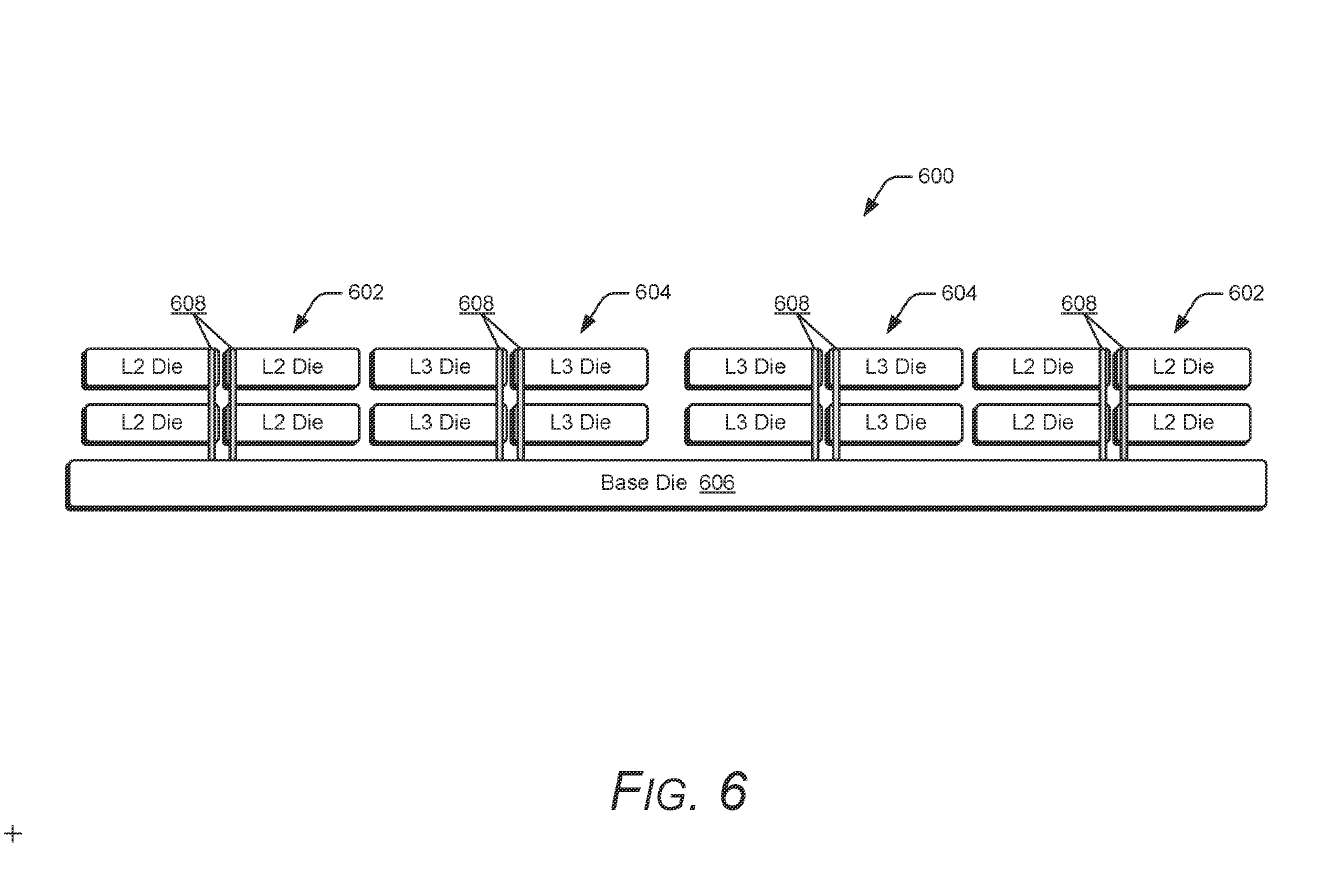

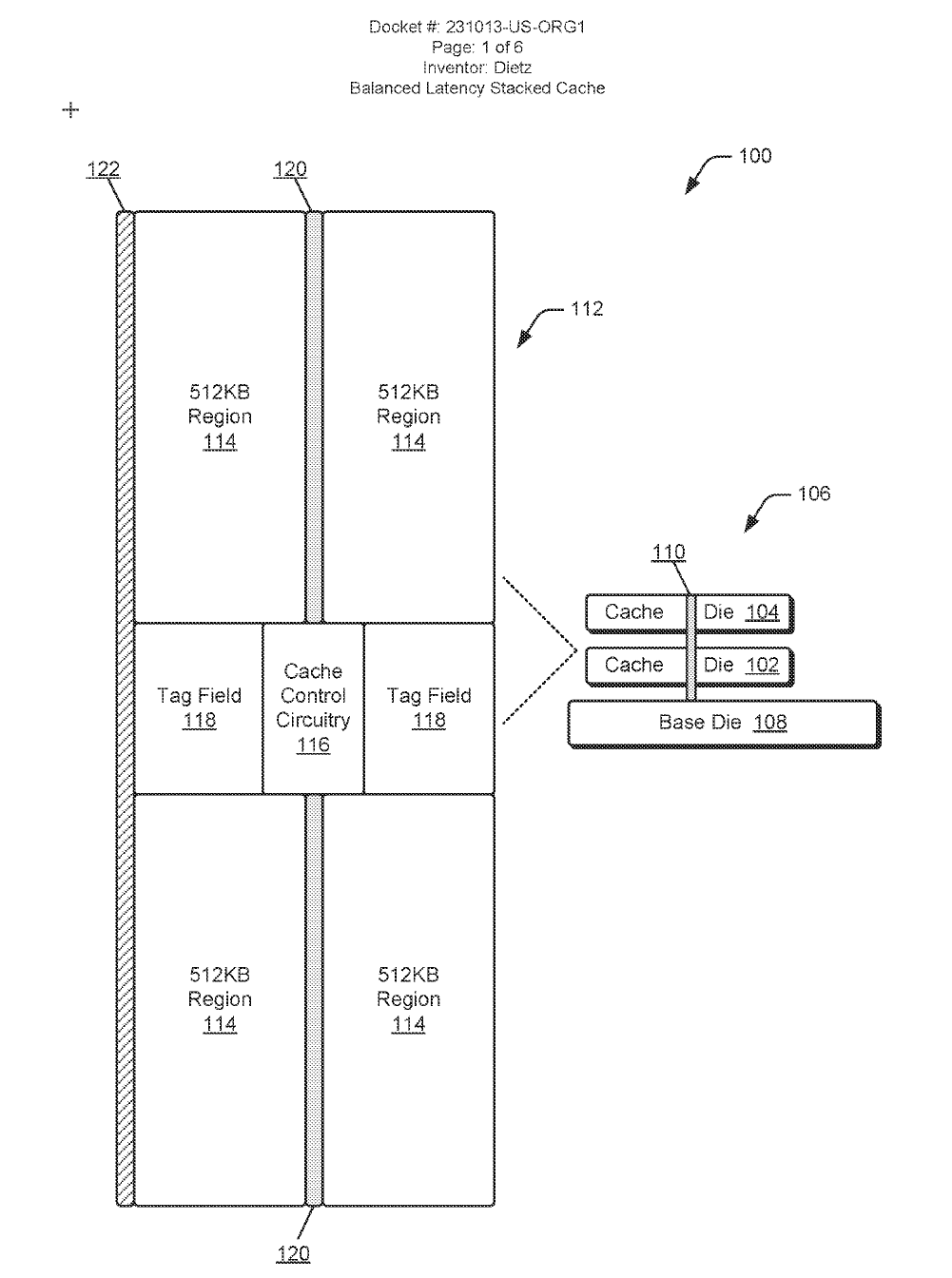

示例图显示,AMD设想了一种多层堆叠结构,基础层连接计算核心与缓存模块,上方可继续叠加多层缓存Die,例如通过四组512KB区域组成的2MB L2模块,甚至可以进一步扩展至4MB。

堆叠方法利用了与3D V-Cache相同的原理,通过硅通孔(TSV)将L2/L3堆叠连接到基础芯片和计算复合体,配置在堆叠缓存系统的中心垂直方向,CCC控制数据输入和输出。

在论文中,AMD使用平面1 MB和2 MB L2缓存配置作为示例指出,平面配置的1 MB L2缓存的典型延迟为14个周期,而堆叠的1 MB L2缓存的延迟为12个周期。

这表明堆叠L2缓存不仅可以提供更高的容量,还可以实现与典型平面方法相似或更好的周期延迟,此外AMD还提到,这种架构具有明显的节省功耗优势。