时隔半年,继“破晓(PoX)”皮秒闪存器件问世,复旦大学在二维电子器件工程化道路上,再获里程碑式突破。日前,复旦大学宣布,该校周鹏-刘春森团队研发的“长缨(CY-01)”架构,将二维超快闪存器件“破晓(POX)”与成熟硅基CMOS工艺深度融合,率先研发出全球首颗二维-硅基混合架构芯片。

相关研究成果以《全功能二维-硅基混合架构闪存芯片》(A full-featured 2D flash chip enabled by system integration)为题,于北京时间10月8日晚间,在《自然》(Nature)期刊上发表。

复旦大学表示,这一突破攻克了新型二维信息器件工程化的关键难题,为新一代颠覆性器件缩短应用化周期提供范例,也为推动信息技术迈入全新高速时代提供强力支撑。

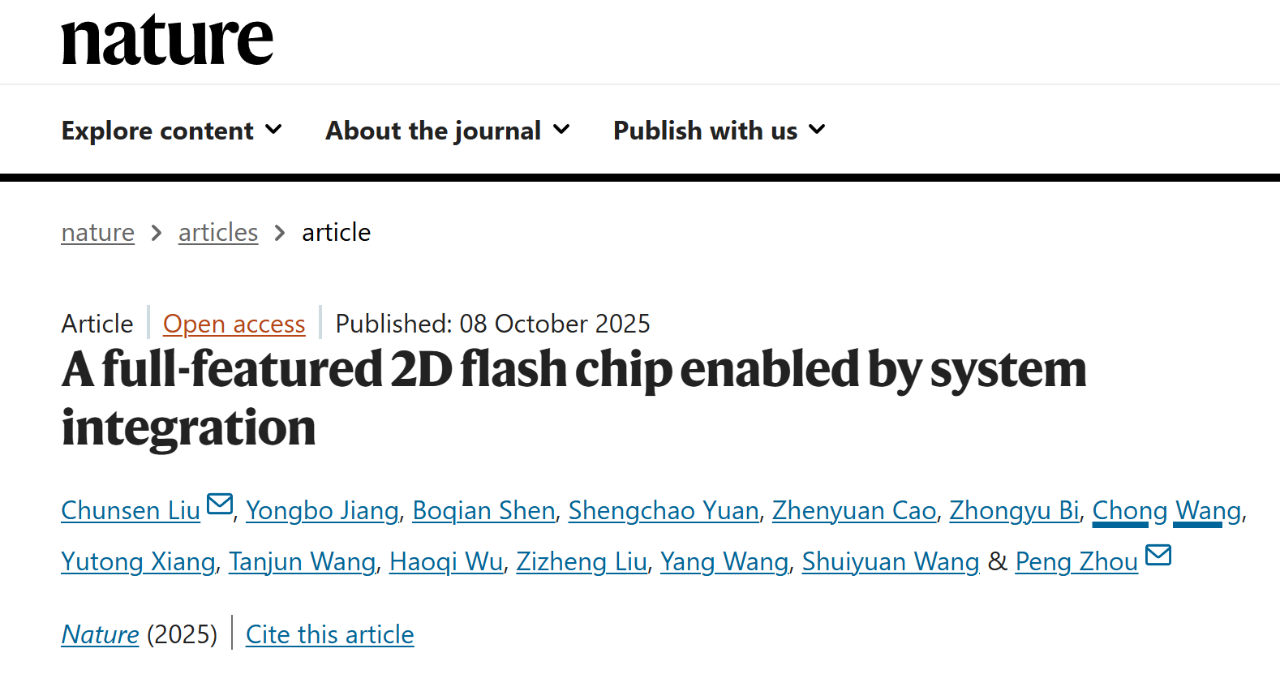

封装后的二维-硅基混合架构闪存芯片(带PCB板)

据介绍,当前,CMOS技术是集成电路制造的主流工艺,市场中的大部分集成电路芯片均使用CMOS技术制造,产业链较为成熟。

团队认为,如果要加快新技术孵化,就要将二维超快闪存器件充分融入CMOS传统半导体产线,而这也能为CMOS技术带来全新突破。

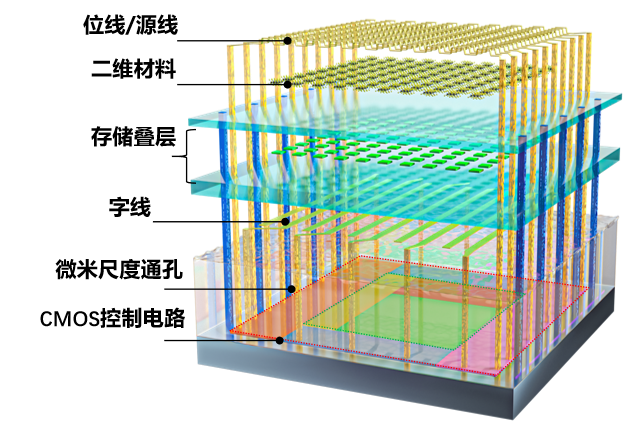

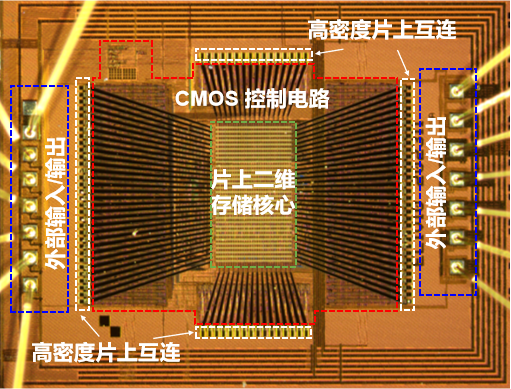

基于CMOS电路控制二维存储核心的全片测试支持8-bit指令操作,32-bit高速并行操作与随机寻址,良率高达94.3%。

这也是迄今为止世界上首个二维-硅基混合架构闪存芯片,性能“碾压”目前的Flash闪存技术,首次实现了混合架构的工程化。

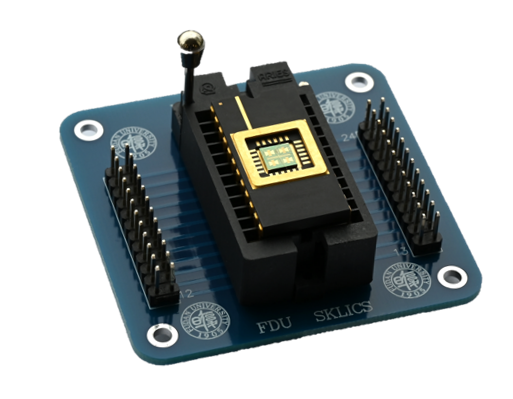

据了解,CMOS电路表面有很多元件,如同一个微缩“城市”,有高楼也有平地,高低起伏。

而二维半导体材料厚度仅有1-3个原子,如同“蝉翼”般纤薄而脆弱,如果直接将二维材料铺在CMOS电路上,材料很容易破裂,更不用谈实现电路性能。

如何将二维材料与CMOS集成又不破坏其性能,是团队需要攻克的核心难题。

团队决定从本身就具有一定柔性的二维材料入手,通过模块化的集成方案,先将二维存储电路与成熟CMOS电路分离制造,再与CMOS控制电路通过高密度单片互连技术(微米尺度通孔)实现完整芯片集成。

二维-硅基混合架构闪存芯片结构示意图,包含二维模块、CMOS控制电路和微米尺度通孔

正是这项核心工艺的创新,实现了在原子尺度上让二维材料和CMOS衬底的紧密贴合,最终实现超过94%的芯片良率。

依托前期完成的研究成果与集成工作,此次打造出的芯片已成功流片。

下一步,团队计划建立实验基地,与相关机构合作,建立自主主导的工程化项目,并计划用3-5年时间将项目集成到兆量级水平,期间产生的知识产权和IP可授权给合作企业。

二维-硅基混合架构闪存芯片光学显微镜照片